## Complex Clocking Situations Using Primetime

Paul Zimmer

(pzimmer@cisco.com)

### Telco chips have:

- Multiplexed clocks

- Falling-, Rising-, and Both-edge clocks

- Divide-by clocks with unusual phase relationships

- Combinations of the above

- Many clocks (one chip had over 200!)

### Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

### Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

## Clock Muxes / Managing large numbers of clocks

- Use check timing to make sure that all clock muxes are controlled

- Use array to deal with false paths between unrelated clocks.

- For details and examples, see paper.

## Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

- Becoming very common.

- Allows for higher speeds, since clock cycle is limited by skew rather than absolute delay.

- Challenge is constraining them in PrimeTime such that timing problem appear as VIOLATIONS.

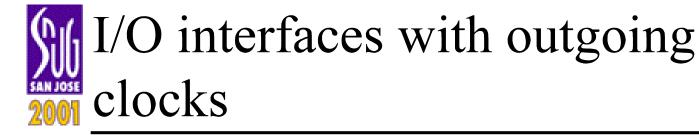

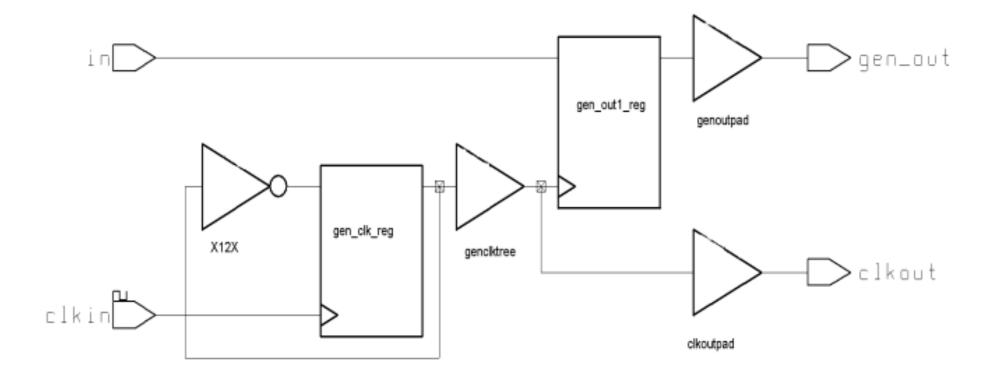

## **Basic Outgoing Clock**

# Outgoing clock code using divide\_by 1

```

create_clock -period 10.0 [get_ports clkin]

set_propagated_clock clkin

create_generated_clock \

-name clkout \

-source [get_ports clkin] \

-divide_by 1 \

[get_ports clkout]

set _gen2src(clkout) clkin

set_output_delay -clock clkout 1.0 gen_out

# Now create a difference in output timing:

set_load 0.5 [get_ports gen_out]

set_load 0.25 [get_ports clkout]

set_annotated_delay -cell -from clkoutpad/A -to clkoutpad/Z -rise 0.3

set_annotated_delay -cell -from clkoutpad/A -to clkoutpad/Z -fall 0.1

```

#### Resulting Timing Report

```

report timing -input pins -path type full clock -to gen out

Startpoint: gen out unbuf reg

(rising edge-triggered flip-flop clocked by clkin)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout

Path Type: max

Point

Incr

Path

clock clkin (rise edge)

0.00

0.00

clock source latency

0.00

0.00

0.00 r

0.00

clkin (in)

0.00

clktree/A (BUFC)

0.00 r

clktree/Z (BUFC)

0.11

0.11 r

0.00

0.00

gen out unbuf reg/CP (FD1QA)

0.11 r

gen out unbuf reg/CP (FD1QA)

0.11 r

gen out unbuf reg/Q (FD1QA)

0.33

0.44 r

genoutpad/A (BUFC)

0.00

0.44 r

qenoutpad/Z (BUFC)

0.42

0.86 r

0.00

0.86 r

gen out (out)

0.86

data arrival time

10.00

10.00

clock clkout (rise edge)

10.41

clock network delay (ideal)

output external delay

9.41

data required time

data required time

9.41

data arrival time

-0.86

8.55

slack (MET)

```

# Where did the "clock network delay" come from?

```

report_timing -delay max_rise -to [get_ports clkout]

```

Startpoint: clkin (clock source 'clkin')

Endpoint: clkout (output port)

Path Group: (none)

Path Type: max

| Point                                  | Incr           | Path             |

|----------------------------------------|----------------|------------------|

| clkin (in)                             | 0.00           | 0.00 r           |

| clktree/Z (BUFC)<br>clkoutpad/Z (BUFB) | 0.11<br>0.30 * | 0.11 r<br>0.41 r |

| clkout (out)<br>data arrival time      | 0.00           | 0.41 r<br>0.41   |

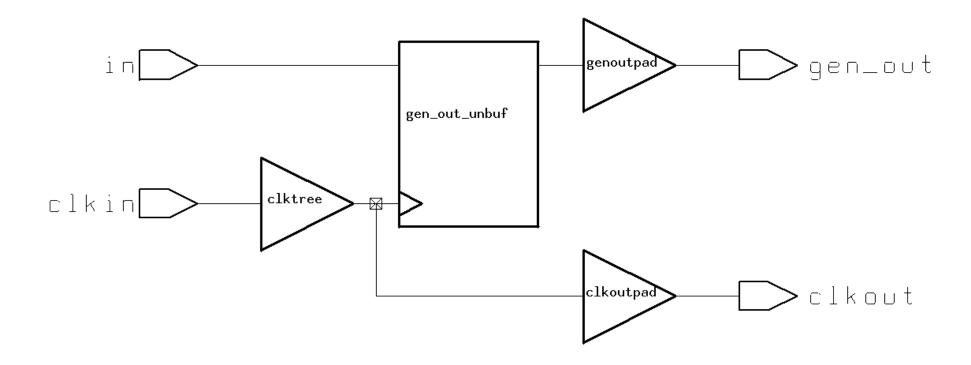

### Divided Outgoing Clock

# Mi Di

#### Divided Outgoing Clock Code

```

create_clock -period 10.0 [get_ports clkin]

set_propagated_clock clkin

# create the div2 clock on the port

create_generated_clock \

-name clkout \

-source [get_ports clkin] \

-divide_by 2 \

[get_ports clkout]

8

# create the div2 clock on the Q pin (so that it gets used for gen_out flop)

create_generated_clock \

-name clkout_at_q \

-source [get_ports clkin] \

-divide_by 2 \

[get_pins gen_clk_reg/Q]

set_propagated_clock clkout_at_q

set_output_delay -clock clkout 1.0 gen_out

# To make the timing report easier to follow, we'll again add some

# loads and delays:

set_load 0.5 [get_ports gen_out]

set_load 0.25 [get_ports clkout]

```

#### Resulting Timing Report

```

report_timing -to [get_ports gen_out] -input_pins -path_type full_clock

```

Startpoint: gen out1 reg

(rising edge-triggered flip-flop clocked by clkout at q)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout Path Type: max

| Point                                                                                                                                                                                                                                                                                | Incr                                                                                 | Path                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) genoutpad/A (BUFC) genoutpad/Z (BUFC) gen_out (out) data arrival time | 0.00<br>0.34<br>8.00<br>0.00<br>0.14<br>0.00<br>0.00<br>0.33<br>0.00<br>0.42<br>0.00 | 0.00<br>0.34<br>0.34 r<br>0.34 r<br>0.48 r<br>0.48 r<br>0.48 r<br>0.82 r<br>0.82 r<br>1.24 r<br>1.24 r |

| clock clkout (rise edge) clock network delay (ideal) output external delay data required time                                                                                                                                                                                        | 0.81<br>-1.00                                                                        | 20.00<br>20.81<br>19.81<br>19.81<br>                                                                   |

| slack (MET)                                                                                                                                                                                                                                                                          |                                                                                      | 18.57                                                                                                  |

## Where do the 0.34 and 0.81 come from?

First, here's where the "clock source latency" of clkout\_at\_q comes from:

The "clock network delay (ideal)" of clkout is this value plus the delay through the genclktree and the clkout pad:

| Point                                                                                                            | Incr                                 | Path                                                 |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|

| clock source latency gen_clk_reg/Q (FD1QA) genclktree/Z (BUFC) clkoutpad/Z (BUFB) clkout (out) data arrival time | 0.34<br>0.00<br>0.14<br>0.33<br>0.00 | 0.34<br>0.34 r<br>0.48 r<br>0.81 r<br>0.81 r<br>0.81 |

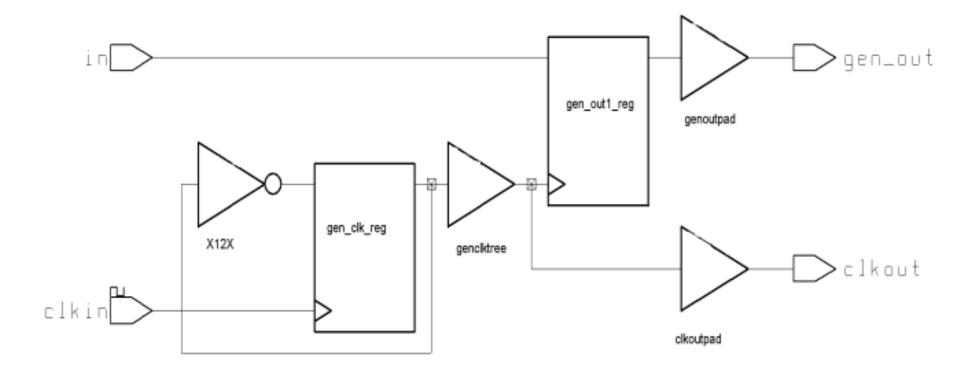

#### Outgoing Inverted Clock

## Outgoing Inverted Clock code

```

create_clock -period 10.0 [get_ports clkin]

set_propagated_clock clkin

# create the div2 clock on the port

create_generated_clock \

-name clkout \

-source [get_ports clkin] \

-divide_by 2 \

-invert \

[get_ports clkout]

# create the div2 clock on the Q pin (so that it gets used for gen_out flop)

create_generated_clock \

-name clkout_at_q \

-source [get_ports clkin] \

-divide_bu 2 \

[get_pins gen_clk_reg/Q]

set_propagated_clock clkout_at_q

set_output_delay -clock clkout 1.0 gen_out

# create a difference in output timing

set_load 0.5 [get_ports gen_out]

set_load 0.25 [get_ports clkout]

```

# Outgoing Inverted Clock timing report

report timing -to [get ports gen out] -input pins -path type full clock

Startpoint: gen\_out1\_reg

(rising edge-triggered flip-flop clocked by clkout at q)

Endpoint: gen\_out (output port clocked by clkout)

Path Group: clkout Path Type: max

| Point                                                                                                                                                                                                                             | Incr                                                         | Path                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) genoutpad/A (BUFC) | 0.00<br>0.34<br>0.00<br>0.00<br>0.15<br>0.00<br>0.34<br>0.00 | 0.00<br>0.34<br>0.34 r<br>0.34 r<br>0.49 r<br>0.49 r<br>0.49 r<br>0.83 r<br>0.83 r |

| genoutpad/Z (BUFC)<br>gen_out (out)<br>data arrival time                                                                                                                                                                          | 0.42                                                         | 1.25 r<br>1.25 r<br>1.25                                                           |

| clock clkout (rise edge)<br>clock network delay (ideal)<br>output external delay<br>data required time                                                                                                                            | 10.00<br>0.77<br>-1.00                                       | 10.00<br>10.77<br>9.77<br>9.77                                                     |

| data required time<br>data arrival time                                                                                                                                                                                           |                                                              | 9.77<br>-1.25                                                                      |

| slack (MET)                                                                                                                                                                                                                       |                                                              | 8.52                                                                               |

# Outgoing Inverted Clock timing report - hold

report\_timing -to [get\_ports gen\_out] -input\_pins -path\_type full\_clock delay min

Startpoint: gen\_out1\_reg

(rising edge-triggered flip-flop clocked by clkout at q)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout Path Type: min

| Point                                                                                                                                                                                                                                                | Incr                                                                  | Path                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) genoutpad/A (BUFC) genoutpad/Z (BUFC) | 20.00<br>0.34<br>0.00<br>0.00<br>0.15<br>0.00<br>0.34<br>0.00<br>0.36 | 20.00<br>20.34<br>20.34 r<br>20.34 r<br>20.49 r<br>20.49 r<br>20.49 r<br>20.83 f<br>20.83 f<br>21.19 f |

| gen_out (out) data arrival time                                                                                                                                                                                                                      | 0.00                                                                  | 21.19 f<br>21.19                                                                                       |

| clock clkout (rise edge)<br>clock network delay (ideal)<br>output external delay<br>data required time                                                                                                                                               | 10.00<br>0.77<br>-1.00                                                | 10.00<br>10.77<br>9.77<br>9.77                                                                         |

| data required time<br>data arrival time                                                                                                                                                                                                              |                                                                       | 9.77<br>-21.19                                                                                         |

| slack (MET)                                                                                                                                                                                                                                          |                                                                       | 11.42                                                                                                  |

## Where does the 0.77ns come from?

```

report timing -to [get ports clkout] -delay max rise

```

Startpoint: gen clk reg/Q

(clock source 'clkout\_at\_q')

Endpoint: clkout (output port)

Path Group: (none)

Path Type: max

| Point                                                                                         | Incr                                 | Path                                         |

|-----------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|

| clock source latency gen_clk_reg/Q (FD1QA) genclktree/Z (BUFC) clkoutpad/Z (N1B) clkout (out) | 0.34<br>0.00<br>0.17<br>0.27<br>0.00 | 0.34<br>0.34 f<br>0.50 f<br>0.77 r<br>0.77 r |

| data arrival time                                                                             |                                      | 0.77                                         |

# What if the external device uses falling edges?

Back to original circuit:

# What if the external device uses falling edges?

Code now has "-clock\_fall":

```

create_clock -period 10.0 [get_ports clkin]

set_propagated_clock clkin

# create the div2 clock on the port

create_generated_clock \

-name clkout \

-source [get_ports clkin] \

-divide_by 2 \

[get_ports clkout]

# create the div2 clock on the Q pin (so that it gets used for gen_out flop)

create_generated_clock \

-name clkout_at_q \

-source [get_ports clkin] \

-divide_bu 2 \

[get_pins gen_clk_reg/Q]

set_propagated_clock clkout_at_q

set_output_delay -clock clkout 1.0 gen_out (-clock_fall

# To make the timing report easier to follow, we'll again add some

# loads and delays:

set_load 0.5 [get_ports gen_out]

set_load 0.25 [get_ports clkout]

```

# External Device uses falling edges - timing report

report\_timing -to [get\_ports gen\_out] -input\_pins -path\_type full\_clock

Startpoint: gen\_out1\_reg

(rising edge-triggered flip-flop clocked by clkout\_at\_q)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout Path Type: max

| Point                                                                                                                                                                                                                                                 | Incr                                                                 | Path                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) gen_outpad/A (BUFC) genoutpad/Z (BUFC) | 0.00<br>0.34<br>0.00<br>0.00<br>0.14<br>0.00<br>0.00<br>0.33<br>0.00 | 0.00<br>0.34<br>0.34 r<br>0.34 r<br>0.48 r<br>0.48 r<br>0.48 r<br>0.82 r<br>0.82 r |

| gen_out (out)<br>data arrival time                                                                                                                                                                                                                    | 0.00                                                                 | 1.24 r<br>1.24                                                                     |

| clock clkout (fall edge)<br>clock network delay (ideal)<br>output external delay<br>data required time                                                                                                                                                | 10.00<br>0.78<br>-1.00                                               | 10.00<br>10.78<br>9.78<br>9.78                                                     |

| data required time<br>data arrival time                                                                                                                                                                                                               |                                                                      | 9.78<br>-1.24                                                                      |

| slack (MET)                                                                                                                                                                                                                                           |                                                                      | 8.54                                                                               |

## Where does the 0.78 ns come from?

| Point                                                                                                     | Incr                                 | Path                                         |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|

| <pre>clock source latency gen_clk_reg/Q (FD1QA) genclktree/Z (BUFC) clkoutpad/Z (BUFB) clkout (out)</pre> | 0.34<br>0.00<br>0.16<br>0.28<br>0.00 | 0.34<br>0.34 f<br>0.50 f<br>0.78 f<br>0.78 f |

| data arrival time                                                                                         |                                      | 0.78                                         |

## CISCO SYSTEMS

#### Setup trace:

report\_timing -to [get\_ports gen\_out] -input\_pins -path\_type full\_clock

Startpoint: gen out1 reg

(rising edge-triggered flip-flop clocked by clkout at q)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout Path Type: max

| Point                                                                                                                                                                                                                                                                                | Incr                                                                                 | Path                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) genoutpad/A (BUFC) genoutpad/Z (BUFC) gen_out (out) data arrival time | 0.00<br>0.34<br>0.00<br>0.00<br>0.15<br>0.00<br>0.00<br>0.34<br>0.00<br>0.42<br>0.00 | 0.00<br>0.34<br>0.34 r<br>0.34 r<br>0.49 r<br>0.49 r<br>0.49 r<br>0.83 r<br>0.83 r<br>1.25 r<br>1.25 r |

| clock clkout (fall edge) clock network delay (ideal) output external delay data required time data required time data arrival time                                                                                                                                                   | 20.00<br>0.68<br>-1.00                                                               | 20.00<br>20.68<br>19.68<br>19.68<br>                                                                   |

| slack (MET)                                                                                                                                                                                                                                                                          |                                                                                      | 18.43                                                                                                  |

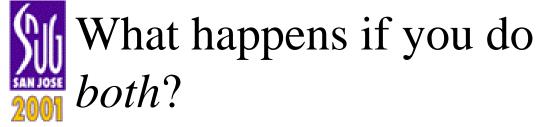

## What happens if you do both?

#### Hold trace:

report\_timing -to [get\_ports gen\_out] -input\_pins -path\_type full\_clock - delay min

Startpoint: gen\_out1\_reg

(rising edge-triggered flip-flop clocked by clkout at q)

Endpoint: gen out (output port clocked by clkout)

Path Group: clkout Path Type: min

| Point                                                                                                                                                                                                                                                              | Incr                                                                                 | Path                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| clock clkout_at_q (rise edge) clock source latency gen_clk_reg/Q (FD1QA) genclktree/A (BUFC) genclktree/Z (BUFC) gen_out1_reg/CP (FD1QA) gen_out1_reg/CP (FD1QA) gen_out1_reg/Q (FD1QA) gen_out1_reg/Q (FD1QA) genoutpad/A (BUFC) genoutpad/Z (BUFC) gen out (out) | 0.00<br>0.34<br>0.00<br>0.00<br>0.15<br>0.00<br>0.00<br>0.34<br>0.00<br>0.36<br>0.00 | 0.00<br>0.34<br>0.34 r<br>0.34 r<br>0.49 r<br>0.49 r<br>0.49 r<br>0.83 f<br>0.83 f<br>1.19 f |

| data arrival time                                                                                                                                                                                                                                                  |                                                                                      | 1.19                                                                                         |

| clock clkout (fall edge)<br>clock network delay (ideal)<br>output external delay<br>data required time                                                                                                                                                             | 0.00<br>0.68<br>-1.00                                                                | 0.00<br>0.68<br>-0.32<br>-0.32                                                               |

| data required time<br>data arrival time                                                                                                                                                                                                                            |                                                                                      | -0.32<br>-1.19                                                                               |

| slack (MET)                                                                                                                                                                                                                                                        |                                                                                      | 1.52                                                                                         |

## And where did the 0.68 come from?

#### • From the *falling* edge of clkout:

| Point                 | Incr | Path   |  |

|-----------------------|------|--------|--|

| clock source latency  | 0.34 | 0.34   |  |

| gen clk reg/Q (FD1QÅ) | 0.00 | 0.34 r |  |

| genclktree/Z (BUFC)   | 0.15 | 0.49 r |  |

| clkoutpad/Z (N1B)     | 0.18 | 0.67 f |  |

| clkout (out)          | 0.00 | 0.68 f |  |

| data arrival time     |      | 0.68   |  |

## Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

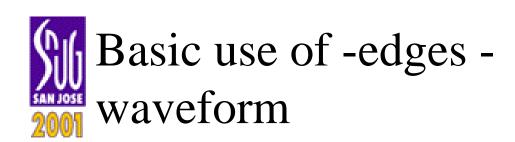

# Describing complex clocking relationships using -edges

- Most common divided clocks can be easily described using the "-divide\_by" option on create\_generated\_clocks.

- Sometimes, this doesn't work particularly if things are happening on

falling edges.

#### Basic use of -edges

# What would happen with divide\_by 2

```

report_timing -to [get_pins ongen_clk_reg/D] -input_pins -path_type

full clock

```

Startpoint: onclk\_reg (rising edge-triggered flip-flop clocked by clkin)

Endpoint: ongen clk req

(rising edge-triggered flip-flop clocked by div2clk)

Path Group: div2clk

Path Type: max

| Point                                                                                                                                                                                                                 | Incr                                   | Path                                                                                        | _             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|---------------|

| clock clkin (rise edge) clock source latency clkin (in) clktree/A (BUFC) clktree/Z (BUFC) onclk_reg/CP (FD1QA) onclk_reg/CP (FD1QA) onclk_reg/Q (FD1QA) onclk_reg/Q (FD1QA) ongen_clk_reg/D (FD1QA) data arrival time | 10.00                                  | 10.00<br>10.00<br>10.00 r<br>10.00 r<br>10.12 r<br>10.12 r<br>10.12 r<br>10.45 f<br>10.45 f | This is wrong |

| clock div2clk (rise edge) clock source latency gen_clk_reg/Q (FD1QA) ongen_clk_reg/CP (FD1QA) library setup time data required time data required time data arrival time                                              | 20.00<br>0.55<br>8.00<br>0.00<br>-0.27 | 20.00<br>20.55<br>20.55 r<br>20.55 r<br>20.29<br>20.29<br>20.29<br>-10.45                   | This is right |

| slack (MET)                                                                                                                                                                                                           |                                        | 9.84                                                                                        | •             |

# Half right – the clock path timing is inverted

```

report_timing =delay max_rise =to gen_clk_reg/CP

```

Startpoint: clkin (clock source 'clkin') Endpoint: gen\_clk\_reg/CP (internal pin)

Path Group: (none)

Path Type: max

| Point                  | Incr | Path                 |

|------------------------|------|----------------------|

| clkin (in)             | 0.00 | 0.00 £               |

| clktree/Z (BUFC)       | 0.16 | 0.15 f               |

| clkinv/Z (NLB)         | 0.04 | 0.20 r               |

| gen_clk_reg/CP (FD1QA) | 0.00 | <del>9.2</del> 0 ± ◀ |

| data arrival time      |      | (0.20)               |

|                        |      |                      |

report\_timing -delay max\_rise -from gen\_clk\_reg/CP -to gen\_clk\_reg/Q

Startpoint: gen clk reg

(rising edge-triggered flip-flop clocked by clkin')

Endpoint: gen clk reg/Q (internal pin)

Path Group: (none)

Path Type: max

| Point                                                          | Incr         | Path                     |

|----------------------------------------------------------------|--------------|--------------------------|

| gen_clk_reg/CP (FD1QA) gen_clk_reg/Q (FD1QA) data_arrival_time | 0.00<br>0.35 | 0.00 r<br>0.35 r<br>0.35 |

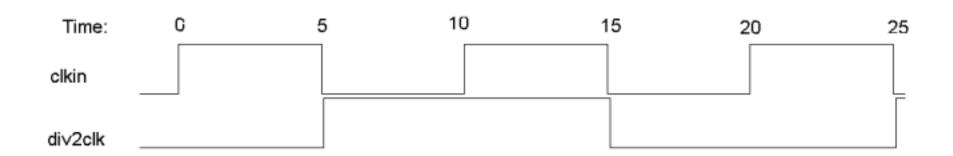

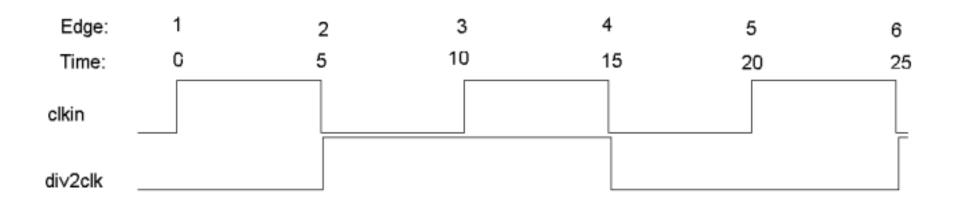

#### Waveform with PT edges marked

#### Script using -edges

```

create_clock -period 10.0 [get_ports clkin]

set_propagated_clock clkin

create_generated_clock \

-name div2clk \

-source [get_ports clkin] \

-edges {2 4 6} \

[get_pins gen_clk_reg/Q]

set_propagated_clock div2clk

```

## Timing report using -edges (setup)

```

report_timing -to [get_pins ongen_clk_reg/D] -input_pins -path_type

full clock

```

Startpoint: onclk\_reg (rising edge-triggered flip-flop clocked by clkin)

Endpoint: ongen\_clk\_reg

(rising edge-triggered flip-flop clocked by div2clk)

Path Group: div2clk

Path Type: max

| Point                                                                                                                                                                                             | Incr                                                                 | Path                                                                               |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------|--------|

| clock clkin (rise edge) clock source latency clkin (in) clktree/A (BUFC) clktree/Z (BUFC) onclk_reg/CP (FD1QA) onclk_reg/CP (FD1QA) onclk_reg/Q (FD1QA) ongen_clk_reg/D (FD1QA) data arrival time | 0.00<br>0.00<br>0.00<br>0.00<br>0.12<br>0.00<br>0.00<br>0.34<br>0.00 | 0.00<br>0.00<br>0.00 r<br>0.00 r<br>0.12 r<br>0.12 r<br>0.12 r<br>0.45 f<br>0.45 f | Right! |

| clock div2clk (rise edge) clock source latency gen_clk_reg/Q (FD1QA) ongen_clk_reg/CP (FD1QA) library setup time data required time data required time data arrival time                          | 8.00<br>0.55<br>0.00<br>0.00<br>-0.27                                | 5.00<br>5.55<br>5.55 r<br>5.55 r<br>5.29<br>5.29<br>5.29<br>-0.45                  | Right! |

| slack (MET)                                                                                                                                                                                       |                                                                      | 4.84                                                                               |        |

### Timing report using -edges (hold)

```

report_timing -to [get_pins ongen_clk_reg/D] -input_pins -path_type

full_clock -delay min

```

Startpoint: onclk\_reg (rising edge-triggered flip-flop clocked by clkin)

Endpoint: ongen\_clk\_reg

(rising edge-triggered flip-flop clocked by div2clk)

Path Group: div2clk

Path Type: min

| Point                                                                                                                                                                                                        | Incr                                                                  | Path                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| <pre>clock clkin (rise edge) clock source latency clkin (in) clktree/A (BUFC) clktree/Z (BUFC) onclk_reg/CP (FD1QA) onclk_reg/CP (FD1QA) onclk_reg/Q (FD1QA) ongen_clk_reg/D (FD1QA) data arrival time</pre> | 10.00<br>0.00<br>0.00<br>0.00<br>0.12<br>0.00<br>0.00<br>0.34<br>0.00 | 10.00<br>10.00 r<br>10.00 r<br>10.02 r<br>10.12 r<br>10.12 r<br>10.45 f<br>10.45 f<br>10.45 |

| clock div2clk (rise edge) clock source latency gen_clk_reg/Q (FD1QA) ongen_clk_reg/CP (FD1QA) ongen_clk_reg/CP (FD1QA) library hold time data required time                                                  | 5.00<br>0.55<br>0.00<br>0.00                                          | 5.00<br>5.55<br>5.55 r<br>5.55 r<br>5.55 r<br>5.72<br>5.72                                  |

| data required time<br>data arrival time                                                                                                                                                                      |                                                                       | 5.72<br>-10.45                                                                              |

| slack (MET)                                                                                                                                                                                                  |                                                                       | 4.74                                                                                        |

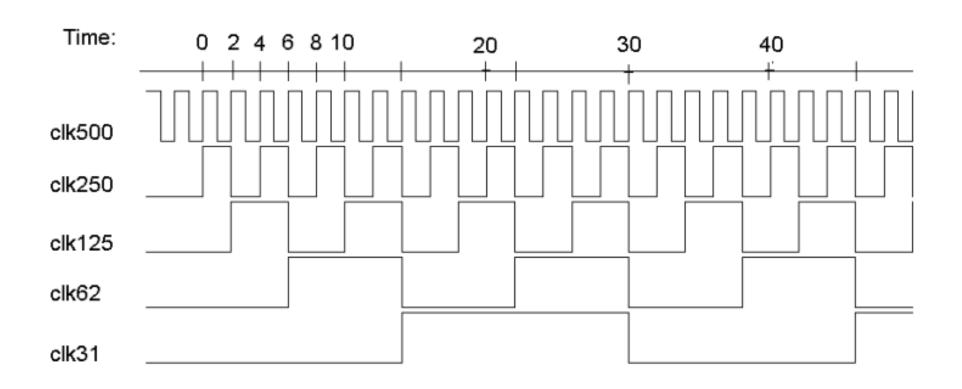

#### More complex use of -edges

```

always @(posedge clk500 or negedge resetL)

begin

if (!resetL)

clk250 <= 0;

else

clk250 <= !clk250;

end

always @(negedge clk250 or negedge resetL) // Note the use of negedge!

begin

if (!resetL)

{clk31,clk62,clk125} <= 0;

else

{clk31,clk62,clk125} <= {clk31,clk62,clk125} + 1;

end</pre>

```

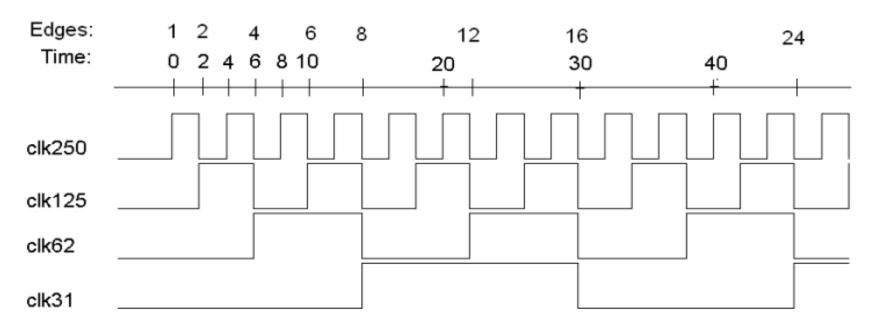

# Complex use of -edges - waveform

# Complex use of -edges - first try

#### • Results in:

- Clk250 is itself a generated clock.

- Generated clocks derived from other generated clocks should always be traced back to their non-generated source.

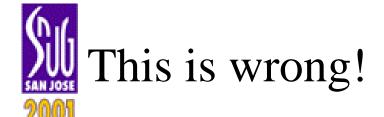

# Complex use of -edges - second try

#### • Results in:

#### This is correct!

```

create_clock -period 2.0 [get_ports clk500]

set_propagated_clock clk500

# create the clk250 on the Q pin using -divide_by

create_generated_clock \

-name clk250 \

-source [get_ports clk500] \

-divide_by 2 \

[get_pins edges/clk250_reg/Q]

set_propagated_clock clk250

# create the divided clocks on the Q pins using -edges

create_generated_clock \

-name clk125 \

-source [get_ports clk500] \

-edges {3 7 11} \

[get_pins edges/clk125_reg/Q]

set_propagated_clock clk125

create_generated_clock \

-name clk62 \

-source [get_ports clk500] \

-edges {7 15 23} \

[get_pins edges/clk62_reg/Q]

set_propagated_clock clk62

create_generated_clock \

-name clk31 \

-source [get_ports clk500] \

-edges {15 31 47} \

[get_pins edges/clk31_reg/Q]

set_propagated_clock clk31

```

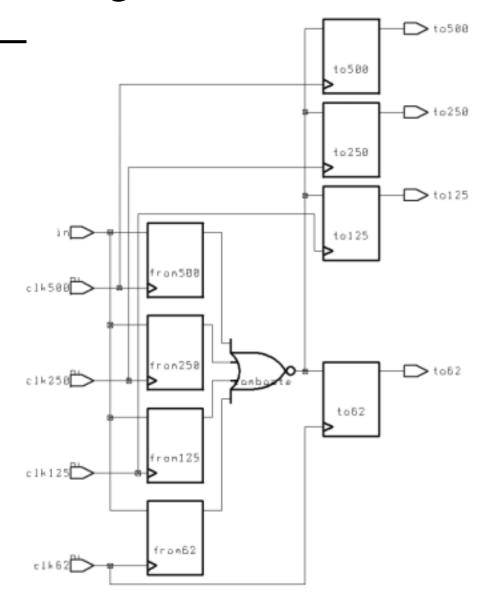

### Complex -edges : test circuit

#### Timing report - clk250 to clk250

report timing -from sampler/from250 reg/Q -to sampler/to250 reg/D

Startpoint: sampler/from250 reg

(rising edge-triggered flip-flop clocked by clk250)

Endpoint: sampler/to250\_reg

(rising edge-triggered flip-flop clocked by clk250)

Path Group: clk250

Path Type: max

| Point                                                                                                                                                                                                           | Incr                                         | Path                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------|

| <pre>clock clk250 (rise edge) clock network delay (propagated) sampler/from250_reg/CP (FD1QA) sampler/from250_reg/Q (FD1QA) &lt;- sampler/combgate/Z (NR4A) sampler/to250_reg/D (FD1QA) data arrival time</pre> | 0.00<br>0.44<br>0.00<br>0.37<br>0.44<br>0.00 | 0.00<br>0.44<br>0.44 r<br>0.81 f<br>1.25 r<br>1.25 r<br>1.25 |

| clock clk250 (rise edge)<br>clock network delay (propagated)<br>sampler/to250_reg/CP (FD1QA)<br>library setup time<br>data required time                                                                        | 4.00<br>0.44<br>-0.28                        | 4.00<br>4.44<br>4.44 r<br>4.16<br>4.16                       |

| data required time<br>data arrival time                                                                                                                                                                         |                                              | 4.16<br>-1.25                                                |

| slack (MET)                                                                                                                                                                                                     |                                              | 2.91                                                         |

#### Timing report - clk125 to clk125

report\_timing -from sampler/from125\_reg/Q -to sampler/to125\_reg/D

Startpoint: sampler/from125 reg

(rising edge-triggered flip-flop clocked by clk125)

Endpoint: sampler/to125 reg

(rising edge-triggered flip-flop clocked by clk125)

Path Group: clk125

Path Type: max

| Point                                                                                                                                                                                             | Incr                                         | Path                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------|

| clock clk125 (rise edge) clock network delay (propagated) sampler/from125_reg/CP (FD1QA) sampler/from125_reg/Q (FD1QA) <- sampler/combgate/Z (NR4A) sampler/to125_reg/D (FD1QA) data arrival time | 2.00<br>1.15<br>0.00<br>0.38<br>0.41<br>0.00 | 2.00<br>3.15<br>3.15 r<br>3.53 f<br>3.94 r<br>3.94 r<br>3.94 |

| clock clk125 (rise edge)<br>clock network delay (propagated)<br>sampler/to125_reg/CP (FD1QA)<br>library setup time<br>data required time                                                          | 10.00<br>1.15<br>-0.27                       | 10.00<br>11.15<br>11.15 r<br>10.88<br>10.88                  |

| data required time<br>data arrival time                                                                                                                                                           |                                              | 10.88<br>-3.94                                               |

| slack (MET)                                                                                                                                                                                       |                                              | 6.94                                                         |

#### Timing report - clk125 to clk62

report\_timing -from sampler/from125\_reg/Q -to sampler/to62\_reg/D

Startpoint: sampler/from125 reg

(rising edge-triggered flip-flop clocked by clk125)

Endpoint: sampler/to62 reg

(rising edge-triggered flip-flop clocked by clk62)

Path Group: clk62 Path Type: max

| Point                                                                                                                                               | Incr                                 | Path                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|

| clock clk125 (rise edge) clock network delay (propagated) sampler/from125_reg/CP (FD1QA) sampler/from125_reg/Q (FD1QA) <- sampler/combgate/Z (NR4A) | 2.00<br>1.15<br>0.00<br>0.38<br>0.41 | 2.00<br>3.15<br>3.15 r<br>3.53 f<br>3.94 r |

| sampler/to62_reg/D (FD1QA)<br>data arrival time                                                                                                     | 0.00                                 | 3.94 r<br>3.94                             |

| clock clk62 (rise edge) clock network delay (propagated) sampler/to62_reg/CP (FD1QA) library setup time data required time                          | 6.00<br>1.10<br>-0.27                | 6.00<br>7.10<br>7.10 r<br>6.83<br>6.83     |

| data required time<br>data arrival time                                                                                                             |                                      | 6.83<br>-3.94                              |

| slack (MET)                                                                                                                                         |                                      | 2.88                                       |

## Timing report - clk125 to clk62 (hold)

$\tt report\_timing - from \ sampler/from 125\_reg/Q - to \ sampler/to 62\_reg/D - delaymin$

Startpoint: sampler/from125\_reg

(rising edge-triggered flip-flop clocked by clk125)

Endpoint: sampler/to62 reg

(rising edge-triggered flip-flop clocked by clk62)

Path Group: clk62 Path Type: min

| Point                                                                                                                                                                                                          | Incr                                          | Path                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------|--|

| <pre>clock clk125 (rise edge) clock network delay (propagated) sampler/from125_reg/CP (FD1QA) sampler/from125_reg/Q (FD1QA) &lt;- sampler/combgate/Z (NR4A) sampler/to62_reg/D (FD1QA) data arrival time</pre> | 10.00<br>1.15<br>0.00<br>0.38<br>0.30<br>0.00 | 10.00<br>11.15<br>11.15 r<br>11.53 r<br>11.83 f<br>11.83 f<br>11.83 |  |

| clock clk62 (rise edge)<br>clock network delay (propagated)<br>sampler/to62_reg/CP (FD1QA)<br>library hold time<br>data required time                                                                          | 6.00<br>1.10<br>0.17                          | 6.00<br>7.10<br>7.10 r<br>7.27<br>7.27                              |  |

| data required time<br>data arrival time                                                                                                                                                                        |                                               | 7.27<br>-11.83                                                      |  |

| slack (MET)                                                                                                                                                                                                    |                                               | 4.56                                                                |  |

### Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

# Phantom Delays on Input and Output Ports

You load up the netlist, read in the sdf, and do report\_timing from some input:

```

report timing -to f1 reg/D

Startpoint: in (input port)

Endpoint: f1 req (rising edge-triggered flip-flop clocked by clkin)

Path Group: (none)

Path Type: max

This should be 0.5!

Point

Incr

Path

Ó.00 r

input external delay

0.00

0.00 r

in (in)

inpad/Z (BUFB)

1.24 r

f1 req/D (FD1QA)

data arrival time

1.24

```

- The "\*" doesn't mean back-annotated, it means "all or part is back-annotated"!

- Do the report\_timing with -input pins:

```

report timing -to f1 reg/D -input pins

Startpoint: in (input port)

Endpoint: f1 reg (rising edge-triggered flip-flop clocked by clkin)

Path Group: (none)

Path Type: max

There's the 0.5 (with a "*"),

Point

Incr

but what's that 0.64?

0.00

0.00 r

input external delay

Ø. 00

in (in)

0.00 r

0.64

inpad/A (BUFB)

inpad/Z (BUFB)

f1 req/D (FD1QA)

data arrival time

1.24

```

### Fixing this using set\_resistance

```

set_resistance 0.0 [get_nets in]

```

Works better than set\_annotated\_delay because it works through hierarchies (see paper for details).

```

report_timing -to f1_reg/D -input_pins

```

Startpoint: in (input port)

Endpoint: fl reg (rising edge-triggered flip-flop clocked by clkin)

Path Group: (none)

Path Type: max

#### Interconnect delay now zero.

| Point                          | Incr     | Path   |

|--------------------------------|----------|--------|

| input external delay           | 0.00     | 0.00 r |

| in (in)                        | 0.00     | 0.00 r |

| pads/in (pads)                 | 0.00     | 0.00 r |

| pads/inpad/A (BUFB)            | ( 0.00 ) | 0.00 r |

| pads/inpad/Z (BUFB)            | 0.50 *   | 0.50 r |

| pads/in buf (pads)             | 0.00 *   | 0.50 r |

| fl reg/ $\overline{D}$ (FD1QA) | 0.10 *   | 0.60 r |

| data arrival time              |          | 0.60   |

### Topics covered in paper

- Clock Muxes / Managing Large Numbers of Clocks

- I/O Interfaces with Outgoing Clocks

- Describing complex clocking relationships using -edges

- Phantom Delays on input and output ports

- Parsing command output for use in a script

## Parsing command output for a value

- Ever want to use a report value in your script?

- get\_timing\_paths works fine for timing values, but what about other report output?

- It can be done!

## Parsing command output - basic flow

- Put report output to a file.

- Execute some shell commands on the file to produce a file that looks like PrimeTime commands ("set variable value").

- Source the file.

## Parsing command output – tcl code

```

# default the variable to zero

set _unconstrained_endpoints 0

set _tempfile "temp[pid]"

set _pt_tempfile "temp[pid].pt"

set _cmd {#!/bin/sh

cat <<END | perl -e '

# Loop over the output looking for lines that match:

Warning: There <some_word> <count> <.*not constrained for maximum delay>

# The <some word> handles "is" or "are".

while (<>) {

if (/Warning: There \S+ (\S+) .*not constrained for maximum delay/) {

# Print out the "set" command

print "set _unconstrained_endpoints $1\n";

}

}

}

Build the executable file

echo $_cmd > $_tempfile

check_timing >> $_tempfile

echo "END" >> $_tempfile

# Make it executable and execute it.

sh chmod +x $_tempfile

sh ./$_tempfile > $_pt_tempfile

# source the resulting output

source $_pt_tempfile

```

#### **Actual check\_timing output**

Warning: There are 2 endpoints which are not constrained for maximum delay.

**Tells shell that input is complete**

### temp.pt file result

```

cr$ cat temp18717.pt

set _unconstrained_endpoints 2

```

Complex clocking situations involving <u>muxes</u>, <u>divided clocks</u>, <u>falling edges</u>, <u>outgoing clocks</u>, and combinations of these do occur in real chips, and PrimeTime can be used to time them correctly – <u>if you</u> <u>know the tricks</u>!